#### An Open-Source HW-SW Codesign Framework for Heterogeneous Multi-Accelerator Compute Clusters

Joren Dumoulin, Ryan Antonio, Xiaoling Yi, Josse Van Delm, Chao Fang, Guilherme Paim and Marian Verhelst

joren.dumoulin@kuleuven.be

#### Outline

- Introduction

- SNAX Framework

- SNAX Cluster

- SNAX-MLIR

- Early Results

- Conclusion

# Obligatory "AI is taking over the world" slide

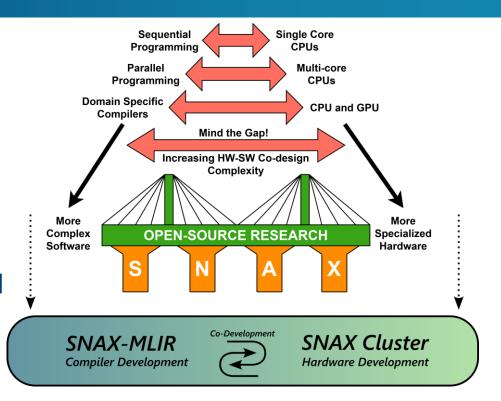

## Software is getting very complex

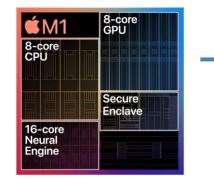

# Hardware is getting specialized and heterogeneous

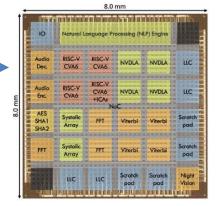

M. C. Dos Santos et al., "14.5 A 12nm Linux-SMP-Capable RISC-V SoC with 14 Accelerator Types, Distributed Hardware Power Management and Flexible NoC-Based Data Orchestration," 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2024, pp. 262-264

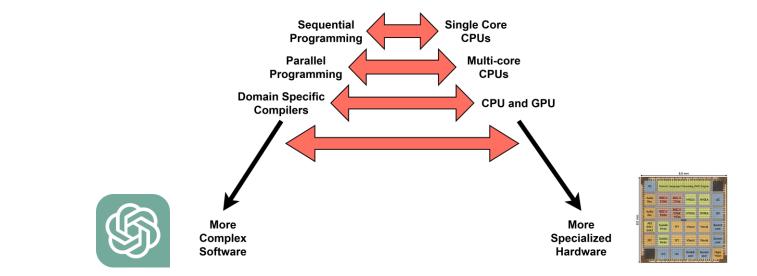

- From single-core CPU

- To multi-core CPU

- To CPU + GPU

- To heterogeneous CPU + GPU + NPU

- To 34-tile 14 accelerator type SoCs!

Image: SoCs

# Deploying complex software on specialized hardware

#### How to bridge this gap? Open-Source Design Frameworks!

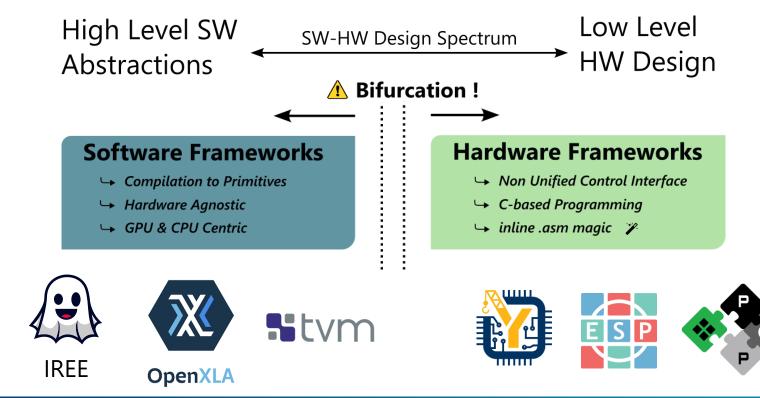

# Existing frameworks

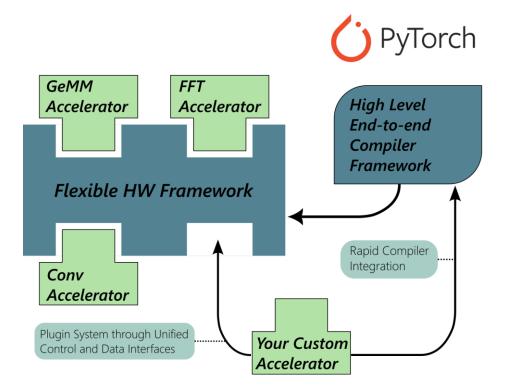

# What is Missing?

- Integrated HW & SW framework with endto-end support

- Rapid plugin system in both Hardware and Software

# SNAX To The Rescue

- SNAX Framework

- Open-Source Design Framework

- Spanning the entire HW-SW spectrum

- Co-Development of Hardware Framework and Compiler Design

#### Outline

- Introduction

- SNAX Framework

- SNAX Cluster

- SNAX-MLIR

- Early Results

- Conclusion

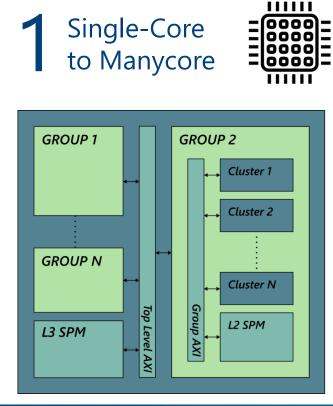

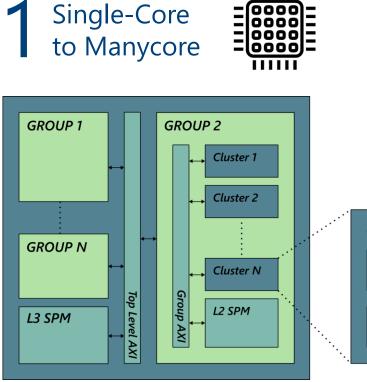

# SNAX Hardware – What are we looking for

#### **SNAX Cluster Design Requirements**

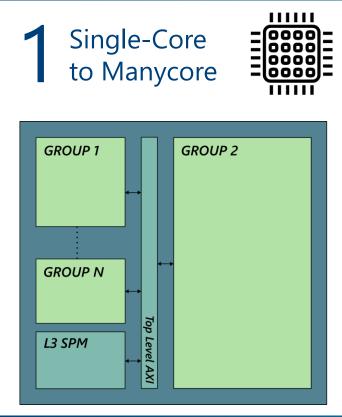

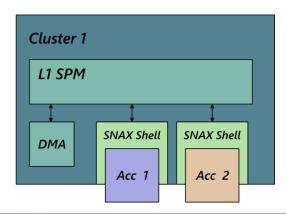

Achieving Flexible, Scalable Manycore systems with PULP! → starting from snitch cluster

https://github.com/pulp-platform/snitch\_cluster

Achieving Flexible, Scalable Manycore systems with PULP! → starting from snitch cluster

https://github.com/pulp-platform/snitch\_cluster

.....

Achieving Flexible, Scalable Manycore systems with PULP! → starting from snitch cluster → RISC-V Cores

https://github.com/pulp-platform/snitch\_cluster

- From Homogenous RISC-V

Cores To Heterogeneous

Accelerators

- Efficiency and Programmability through SNAX Shell

- SNAX =

Snitch Accelerator eXtension!

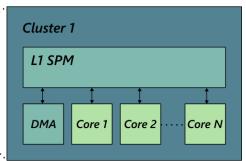

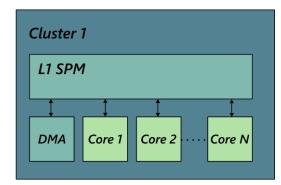

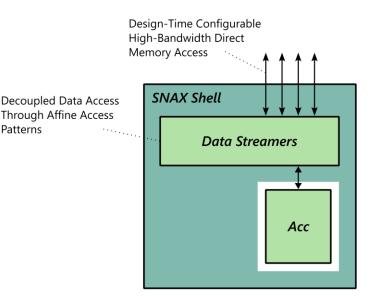

Efficiency through tight data coupling:

- Efficiency follows from efficient data movement & access.

- Decoupled direct data access through standard data streamers

- Connection to memory through configurable high-bandwidth connections

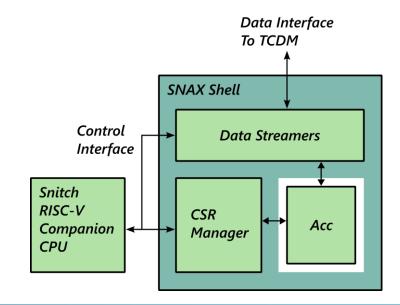

Programmability through loose control coupling:

- Snitch Companion CPU

- Decoupled Control through CSR Manager

- Decoupled Access

- Uniform, reusable components

#### Outline

- Introduction

- SNAX Framework

- SNAX Cluster

- SNAX-MLIR

- Early Results

- Conclusion

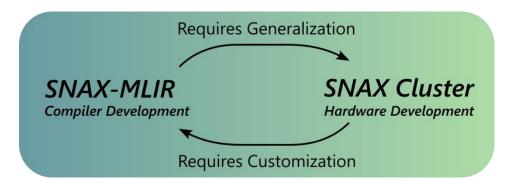

#### **SNAX-MLIR Design Requirements**

2 End-to-end Capabilities

Diverse AcceleratorO□Support▲○

To Achieve Diverse Accelerator Support:

- Generalization

- Customization

- Diverse AcceleratorO□Support△○

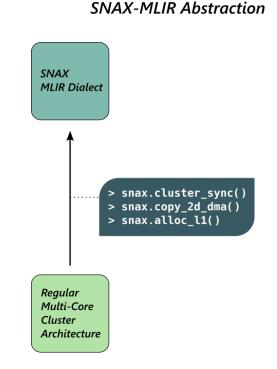

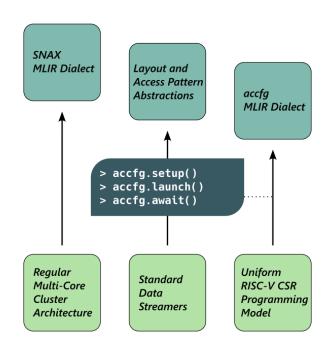

- 1. Raise Generalizations to the Compiler Abstractions

- Multi-Core Cluster Architecture

SNAX Cluster Generalization

- Diverse AcceleratorO□Support△○

- 1. Raise Generalizations to the Compiler Abstractions

- Multi-Core Cluster Architecture

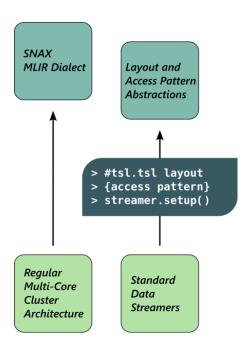

- SNAX Shell Components:

- Data Streamers

SNAX-MLIR Abstraction

#### SNAX Cluster Generalization

- Diverse AcceleratorO□Support▲○

- 1. Raise Generalizations to the Compiler Abstractions

- Multi-Core Cluster Architecture

- SNAX Shell Components:

- Data Streamers

- RISC-V CSR Controller

SNAX-MLIR Abstraction

#### SNAX Cluster Generalization

- 1Diverse AcceleratorO□Support△○

- 2. Customization through Plugin Systems

- SNAX Accelerator Abstraction

- Hardware Developer Friendly Plugin System for Rapid Customization

#### SNAX Accelerator Base Class

Customization Through Plugin System

#### **Custom Functionalities**

- > operator specification

- > programming customization

- > access pattern specification

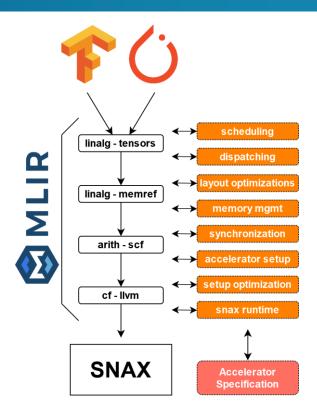

SNAX-MLIR For End-To-End ML Model Deployment on Accelerator Hardware

End-to-end Capabilities

# MLIR Compiler Framework:

- End-to-end: available frontends for many languages and ML frameworks

- **Extensible** through custom dialects

- **Multi-level** for effective highlevel transformations

#### Outline

- Introduction

- SNAX Framework

- SNAX Cluster

- SNAX-MLIR

- Early Results

- Conclusion

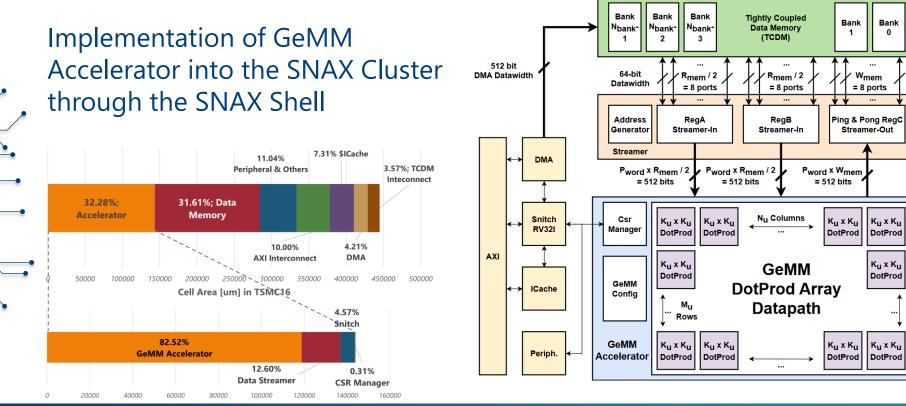

# GeMM Accelerator Case Study

SNAX: An Open-Source HW-SW Codesign Framework for Heterogeneous Multi-Accelerator Compute Clusters

# GeMM Accelerator Case Study

# Compilation from high-level representation

Automatically handled:

- Cluster Data Movements

- Multi-Core Synchronization

- Data Layout Optimizations

- On-the-fly layout transformations

- => >90% utilization on wide variety of matrix dimensions

```

func.func @simple_matmul (

%arg0: memref<64x64xi8>,

%arg1: memref<64x64xi8>,

%arg2: memref<64x64xi8>

```

```

linalg.matmul ins(%arg0, %arg1) outs(%arg2) -> ()

```

#### Outline

- Introduction

- SNAX Framework

- SNAX Cluster

- SNAX-MLIR

- Early Results

- Conclusion

# **Conclusion Slide**

- SNAX aims to be a design framework for heterogeneous multi-core accelerator clusters of the future.

- Through co-development of the HW and SW stack, we aim to create an end-to-end extendable framework, allowing for small contributions to be integrated into a full design.

#### Come and have a look!

#### https://github.com/kuleuven-micas/snax\_cluster https://github.com/kuleuven-micas/snax-mlir