### Fast, Accurate, and Novel Performance Evaluations with PinCPU

#### OSCAR Workshop @ ISCA • June 21, 2025

Nicholas Mosier,<sup>1</sup> Hamed Nemati,<sup>2</sup> John C. Mitchell,<sup>1</sup> Caroline Trippel<sup>1</sup>

<sup>1</sup> Stanford University <sup>2</sup> KTH Royal Institute of Technology

# Detailed end-to-end simulation of modern benchmarks in gem5 is intractible.

gem5 is a popular open-source cycle-accurate, execute-in-execute computer architecture simulator.

F SPEC CPU2017 contains >160 trillion instructions total + gem5's O3CPU simulates ≈140 KIPS on host

> 36 host CPU-years to simulate all of SPEC CPU2017 with O3CPU

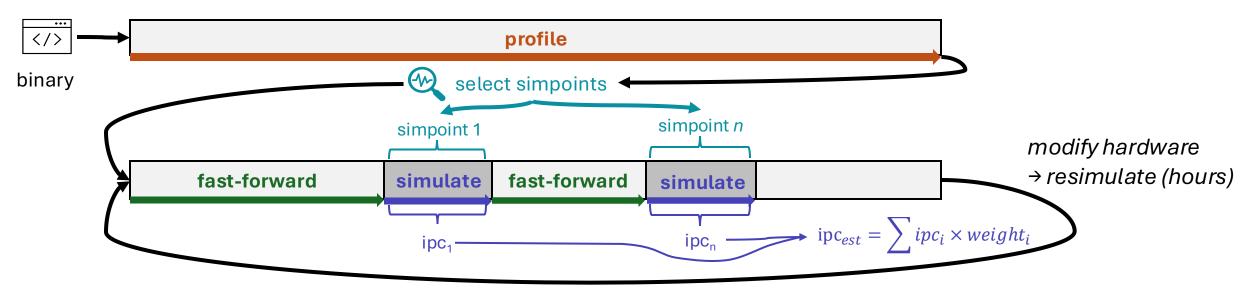

### Solution: SimPoint

[Perelman+ SIGMETRICS'03]

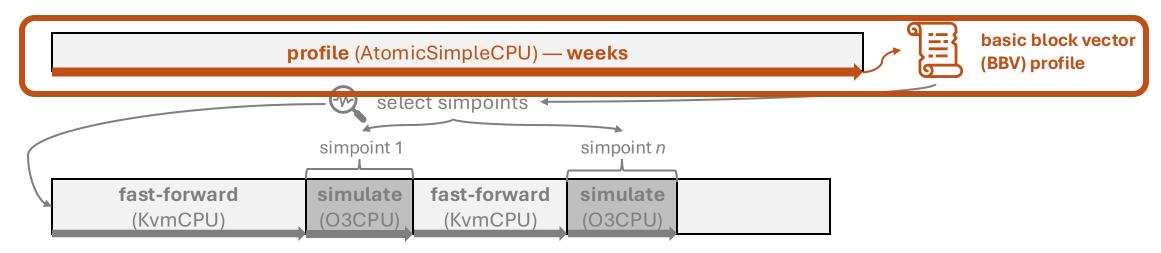

**SimPoint** is a phased-based sampling technique:

- 1. Profile the workload using AtomicSimpleCPU (weeks)

- 2. Select ≤k representative regions (simpoints) (seconds)

- 3. Fast-forward to each simpoint using KvmCPU (minutes)

- 4. Simulate each simpoint using O3CPU (hours)

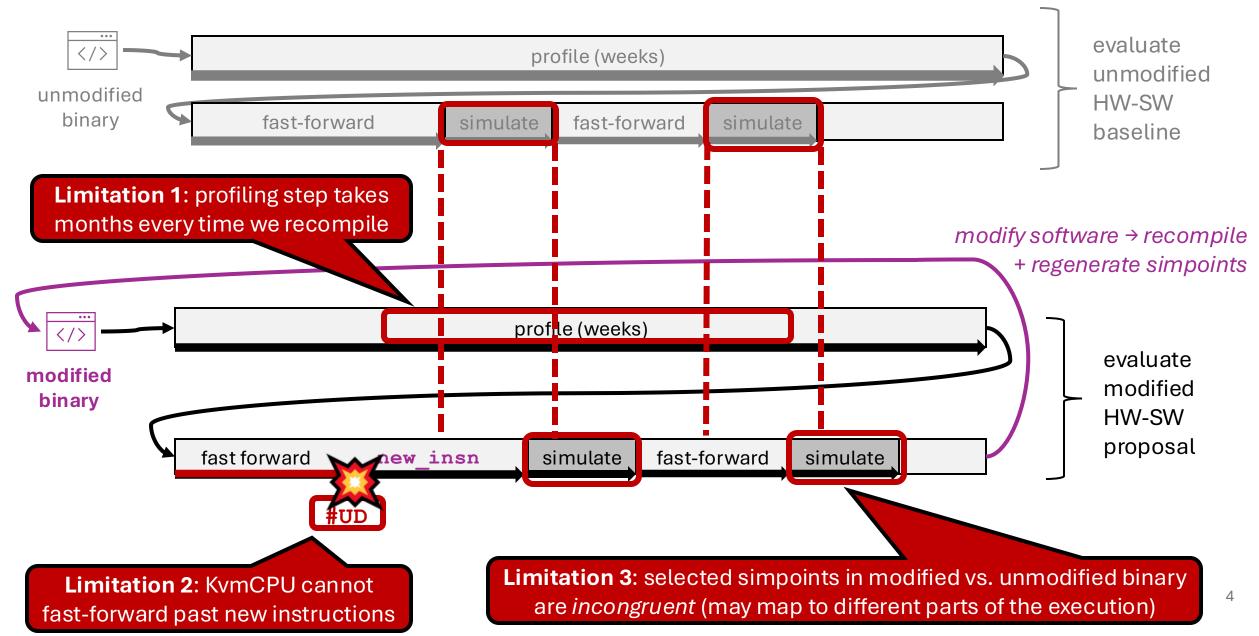

Can we use SimPoint to evaluate hardware-software co-designs in gem5?

#### SimPoint for HW-SW co-design

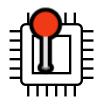

### We present PinCPU: gem5's first fast-forwarding CPU model to support dynamic binary instrumentation.

**Limitation 1**: profiling step takes months every time we recompile

We can resolve all these limitations if gem5 could **dynamically instrument the execution**...

**Limitation 2**: cannot fast-forward past new instructions

Key observation:

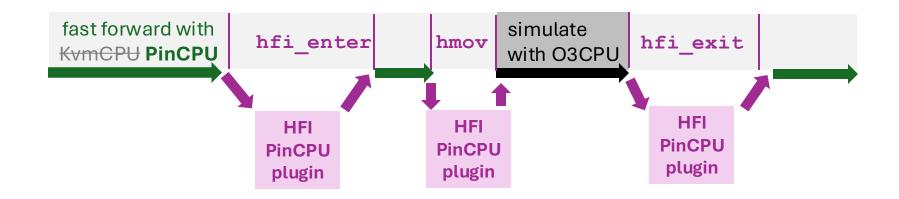

**Limitation 3:** selected simpoints in modified vs. unmodified binary map to different parts of the execution

### **PinCPU** uses Intel Pin [Luk+ PLDI'05] to allow gem5 users to both **fast-forward** and **dynamically instrument** userspace workloads.

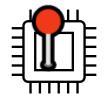

#### Recall Limitation 1: slow simpoint generation

A basic block vector (BBV) counts the dynamic executions of each basic block

in a given *n*-instruction interval. Collection method:

- Official: AtomicSimpleCPU SimPoint probe A slow

- Unofficial: valgrind's BBV profiler

unreliable (due to different HW capabilities, address space layout, syscall behavior, ...) → divergent execution paths → BBV misalignment

Solution: develop a PinCPU plugin

### **BBV Plugin** for fast + accurate simpoint generation: *Plugin code (simplified)*

BBV plugin

src/cpu/pin/tools/bbv.cc(124LoC) configs/pin-bbv.py std::map<ADDRINT, uint64 t> bbv; ļ≣i configuration script void analyze(uint64\_t &count) { ++count; } send command: "bbv dump" void instrument(BBL bbl) { BBL InsertCall(bbl, analyze, &bbv[BBL Address(bbl)]); gem5 PinCPU (syscall emul.) ff model call Analyze() whenever a struct BBVPlugin final : PinCPUPlugin { basic block is executed void reg() override { BBL AddInstrumentFunction(instrument); Pin VM workload override { "{1:42, 2:2, 10: plug-in interface 160, 14:220, ...}" register instrumentation callbacks using Intel Pin API

} plugin;

## **BBV Plugin** for fast + accurate simpoint generation: *Usage (simplified)*

## **BBV Plugin** slowdown vs. AtomicSimpleCPU BBV probe and valgrind BBV profile (SPEC CPU2017 intspeed ref)

\* estimated (extrapolated from prefix of first benchmark input)

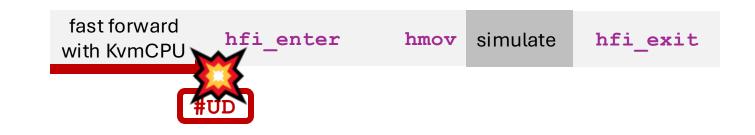

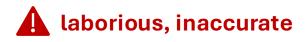

#### Recall Limitation 2: can't fast-forward past new instructions

Hardware Fault Isolation (HFI) [Narayan+ ASPLOS'23] introduces new sandbox instructions:

- **hfi\_enter**: enter sandbox

- hfi\_exit: exit sandbox

- hmov: sandboxed load/store

- Workaround: write standalone emulator to roughly approximate performance on host [Narayan+ ASPLOS'23]

- Workaround: trap+emulate with KvmCPU

#### HFI Plugin for ISA extension emulation

Our HFI plugin for PinCPU hooks onto hfi\_enter, hmov, hfi\_exit and emulates them, rather than executing them directly.

### Recall Limitation 3: incongruent simpoints

- **Problem**: evaluating unmodified baseline and HW-SW proposal on different regions of the workload.

- Solution: SimPoint Translation plugin for PinCPU

13

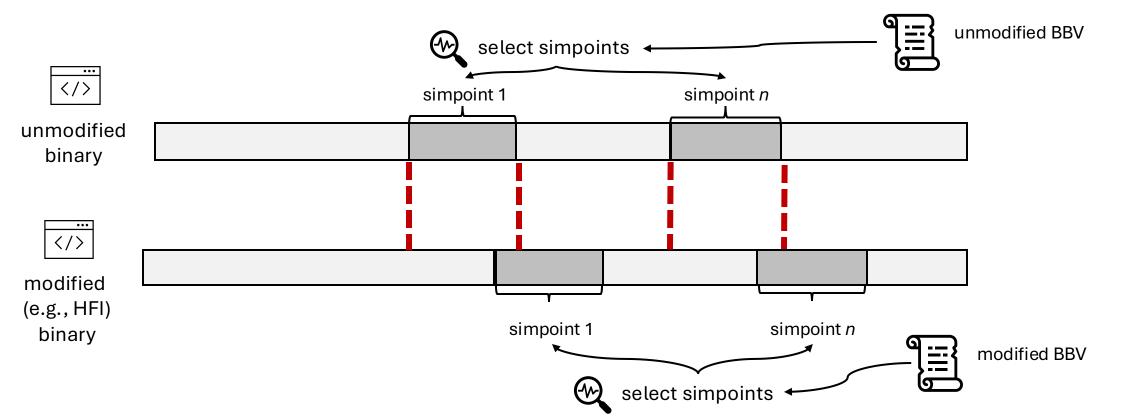

# **SimPoint Translation Plugin** translates unmodified binary simpoints to modified binary

- Use stable source locations as an indicator of forward progress

- **stable** = executes same number of times in both binaries

- stable source locations are collected using BBV plugin + offline analysis

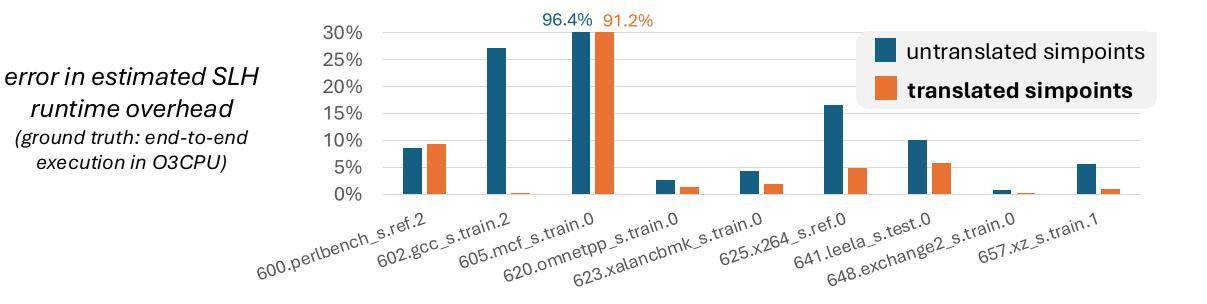

## **SimPoint Translation Plugin**: error of estimated SLH overhead on gem5 O3CPU for SPEC CPU2017 intspeed

Speculative load hardening (SLH) [Carruth LLVM'18] is a software-only Spectre defense that involves heavy program transformation.

Simpoint translation reduces error by >50% on average! **Putting it all together**: PinCPU + our 3 plugins enable fast+accurate hardware-software co-evaluation in gem5

- Hardware-software co-evaluation: comparison of two proposals, at least one of which modifies {software, hardware}

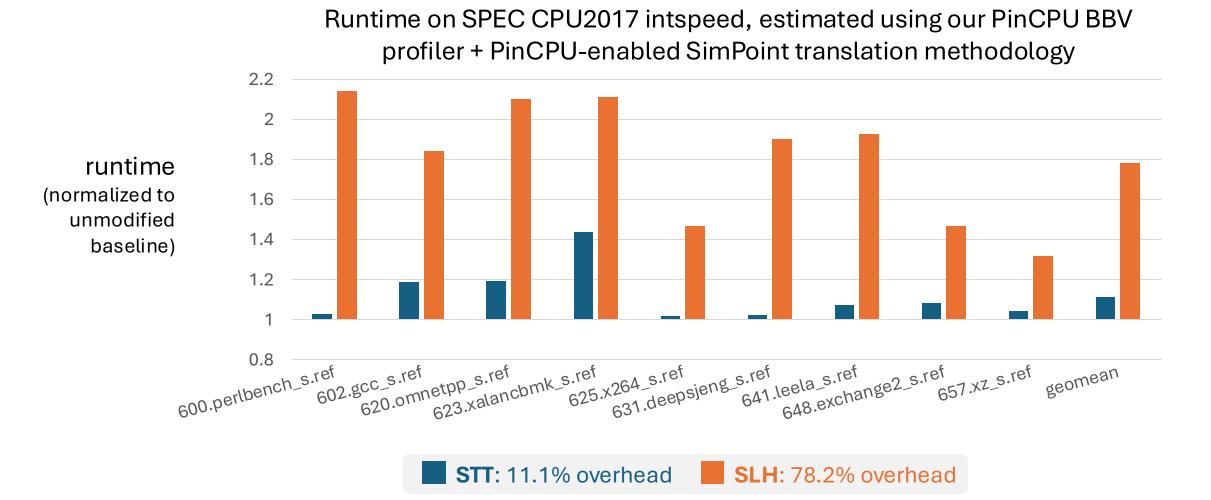

- Co-evaluation #1: Spectre defenses

- Hardware: STT [Yu+ MICRO'19]

- Software: SLH [Carruth LLVM'18], retpoline [GPZ'18]

- Co-evaluation #2: Sandboxing proposals

- Hardware-software: HFI [Narayan+ ASPLOS'23]

- Software: Segue [Narayan+ ASPLOS'25]

- These proposals have never been compared before

### Co-evaluation #1: Spectre defenses

**STT outperforms SLH** while offering stronger security guarantees → hardware-supported Spectre defenses well worth the performance-complexity trade-off.

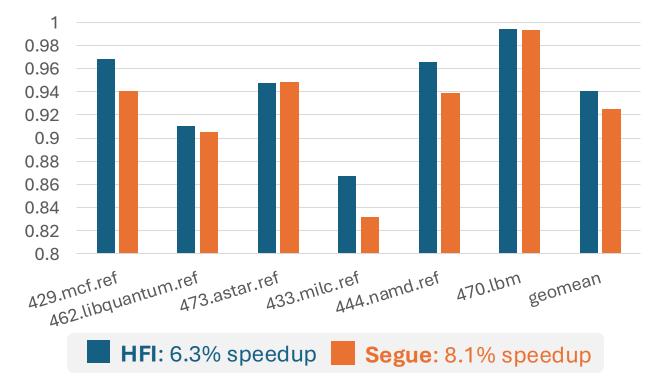

### Co-evaluation #2: Sandboxing proposals

Runtime on SPEC CPU2006, estimated using our PinCPU BBV profiler + HFI plugin + PinCPU-enabled SimPoint translation methodology

Segue (software-only) outperforms HFI (hardware-software) → HFI not worth the performance/complexity trade-off?

\* only WebAssembly-compatible benchmarks evaluted

18

### **Other Features & Limitations**

- Features:

- PinCPU supports checkpointing

- Semantic breakpoints: "stop after instruction 0x1234 executes 100 times"

- Limitations (as of this presentation):

- Only supports syscall emulation (SE) mode, but not gem5 full system (FS) mode

- Doesn't support multithreaded workloads

- Only supports x86-64 ISA

- Future work:

- PinCPU with full system mode: trap+emulate?

- Add multi-threading support

- Add other DBI backends (e.g., DynamoRIO) to support more ISAs

### Conclusion

- PinCPU is the **first** gem5 CPU model to support both **fastforwarding** and **dynamic binary instrumentation**.

- PinCPU plugins allow gem5 users to quickly profile workloads, emulate new instructions, and develop new evaluation methodologies.

- Our three example PinCPU plugins make it possible to perform fast and accurate hardware-software co-evaluations in gem5.

Email: nmosier@stanford.edu

GitHub: github.com/StanfordPLArchSec/pincpu-gem5